# SIMF: Single-Instruction Multiple-Flush Mechanism for Processor Temporal Isolation

Tuo Li<sup>†</sup>, Bradley Hopkins<sup>‡</sup>, and Sri Parameswaran<sup>†</sup> <sup>†</sup>School of Computer Science and Engineering, University of New South Wales, Australia {tuoli,sri.parameswaran}@unsw.edu.au <sup>‡</sup>Defence Science and Technology Group, Edinburgh, Australia {brad.hopkins}@dst.defence.gov.au

# ABSTRACT

Microarchitectural timing attacks are a type of information leakage attack, which exploit the time-shared microarchitectural components, such as caches, translation look-aside buffers (TLBs), branch prediction unit (BPU), and speculative execution, in modern processors to leak critical information from a victim process or thread. To mitigate such attacks, the mechanism for flushing the on-core state is extensively used by operating-system-level solutions, since core-level state is too expensive to partition. In these systems, the flushing operations are implemented in software (using cache maintenance instructions), which severely limit the efficiency of timing attack protection.

To bridge this gap, we propose specialized hardware support, a single-instruction multiple-flush (SIMF) mechanism to flush the core-level state, which consists of L1 caches, BPU, TLBs and register file. We demonstrate SIMF by implementing it as an ISA extension, i.e., FLUSHX instruction, in scalar in-order RISC-V processor. The resultant processor is prototyped on Xilinx ZCU102 FPGA and validated with state-of-art seL4 microkernel, Linux kernel in multi-core scenarios, and a cache timing attack. Our evaluation shows that SIMF significantly alleviates the overhead of flushing by more than a factor of two in execution time and reduces dynamic instruction count by orders-of-magnitude.

## 1. INTRODUCTION

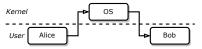

One of the fundamental techniques to secure computer program execution is the confinement of programs to eliminate or minimize information leakage [25]. To improve computing performance, contemporary computer systems contain increasingly complex architectures and microarchitectures (shown in Figure 1), which allows for the time-sharing of hardware (much of the hardware is shared with multiple processes), faster memory references, reduced branch penalty etc. These architectural improvements provide unique opportunities for an adversary to orchestrate advanced information leakage attacks upon modern processing systems [9, 17].

Microarchitectural timing attack (MTA) is an information leakage attack which has been recently shown to be successful [8]. Example exploits include, Meltdown [27] and Spectre [24], which were mounted by taking advantage of branch prediction, speculative execution, and caches.

(a) Process switch (Alice  $\rightarrow$  Bob) in a processor core

(b) Leakage from persistent state at core level. Grey color denotes residual state of the victim Alice;  $t_i$ : time slice *i*.

## Figure 1: Information leakage in time-shared hardware.

In such an attack, the adversary typically relies on the temporal interference of the persistent state in certain microarchitectural components (such as cache) of processors, to create timing variations (e.g., cache access time difference). Such timing variations, along with a priori knowledge of the victim system (software and hardware), can be used to infer the secret data in a time-shared system's hardware [42].

In order to mitigate MTA, existing hardware-based techniques focus on redesigning the cache (which targets cache timing attack) as well as adding information flow tracking across a processor by drastically modifying the processor architecture, which must be created with a corresponding new hardware description language. Software-based techniques at hypervisor or OS level seek to maximally close the cache timing channels by cache partitioning (at shared caches), cache flushing (at private caches). To mitigate MTA system-wide (including all the possible timing channels in multiple microarchitectural states), software-based methods, such as *temporal isolation* (or, time protection) [13] propose the flushing of all on-core states, including private caches, translation look-aside buffers, branch prediction unit, etc.

Recent software-based methods [13, 31, 44] heavily rely on the flushing mechanism. While *flushing or cleansing* the persistent state of multiple vulnerable hardware components at the core level (within Level 1) is regarded as indispensable for creating sound and complete temporal isolation systemwide, these studies have also shown the incompetency of the flushing instructions provided by the existing ISAs, in particular when flushing must be performed frequently (up to 50 KHz). The limitations of the existing hardware support for flushing are discussed in-depth in §3.3 and summarized as the follows: 1) as shown in Figure 2 numerous lines of instructions are used to create routines or functions for flushing each and every microarchitectural component of interest in sequence (sequence is enforced by inserting explicit barrier instructions in between the flushing instructions); and, 2) individual instructions used for flushing may not contain all necessary components, for example, x86 provides one instruction to flush the entire cache hierarchy but lacks a dedicated L1 cache flushing instruction or an instruction to flush the branch prediction unit. As elaborated in §2 and §3 (Figure 3), in our initial estimation, flushing at high frequency can incur more than 30% of additional dynamic instructions, which is equivalent to significant execution time and power overhead (instruction fetch power takes approximately 30% of CPU power [5]).

In this paper, we aim to create one individual specialized flushing instruction to raise the efficiency of temporal isolation at the core level for on-core state towards minimizing the existing and potential timing channels [14]. Based on this instruction, we also aim to explore the upper-bounds of the set of software-based MTA mitigations, which are constructed on top of the flushing mechanism, in terms of efficiency.

To this end, we first propose a single-instruction multipleflushing (SIMF) scheme, which integrates flushing operations in a single instruction to clear the core-level state. The key advantage of SIMF is: 1) sharply reducing the dynamic instruction count (leading to cycle counts and instruction fetch power) dedicated to flushing; 2) minimal extension (adding one instruction to ISA) to the existing hardware; 3) implicitly enforcing the orders of flushing operations in one instruction, without using explicit barrier instructions; 4) programming benefits, including strong atomicity, which cannot be interrupted in the middle (for the case discussed in [44]) and simplicity.

For thoroughly investigating SIMF, we prototyped SIMF in an open-source scalar in-order RISC-V<sup>1</sup> processor. We extended RISC-V ISA with one additional instruction called FLUSHX, which flushes the core-level state including L1/L2 TLBs, L1 caches, branch prediction unit (BTB, RAS, BHT). We also explored flushing the register file, which has been reported as a potential information leakage target [8]. Our evaluation shows that SIMF significantly alleviates the overhead of flushing by more than a factor of two in execution time and reduces dynamic instruction count by orders-ofmagnitude.

The main contributions of this paper are as follows:

An instruction extension, which can flush L1 caches, TLBs, BPU, and register file in one instruction execution;

```

void cleanInvalidateL1Caches(void){//flush L1 caches

dsb():

2

cleanInvalidate_D_PoC();

3

dsb():

4

invalidate_I_PoU();

dsb();

void cleanInvalidate_D_PoC(void){//flush L1 D-cache

8

int clid = readCLID();

9

int loc = LOC(clid);

10

11

int 1;

for (1 = 0; 1 < loc; 1++) {

12

if (CTYPE(clid, 1) > ARMCacheI) {

13

word_t s = readCacheSize(1, 0);

14

int lbits = LINEBITS(s);

15

int assoc = ASSOC(s);

16

17

int assoc_bits = wordBits - clzl(assoc - 1);

int nsets = NSETS(s);

18

19

int w:

for (w = 0; w < assoc; w++) {

20

21

int s;

for (s = 0; s < nsets; s++) {

22

cleanInvalidateByWSL((w << (32 - assoc_bits))</pre>

23

| (s << lbits) | (l << 1));

33333

24

static inline void invalidate I PoU(void){//flush L1 I-cache

25

asm volatile("ic_iallu");

26

27

isb():

28

3

```

Figure 2: Source code of the key functions for ARMv8 processor L1 cache flush in a contemporary operating system microkernel [23] (https://sel4.systems/).

- A FPGA prototype of SIMF in multi-core RISC-V processor;

- Integration of SIMF in state-of-art seL4 microkernel and Linux kernel;

- An evaluation with seL4 kernel, Linux kernel (multicore), and Prime+Probe cache timing attack, on FPGA.

# 2. MOTIVATIONAL EXAMPLE

# 2.1 seL4's L1 Flush with ARM ISA

Figure 2 presents the code snippet of software functions, which perform flushing L1 caches for temporal isolation in the seL4 microkernel, which targets the ARMv8 architecture. In seL4, cleanInvalidateL1Caches (Line 1-8) is called for flushing L1 caches. This function is composed of two major steps, which are essentially two function calls: one for flushing L1 data cache (cleanInvalidate\_D\_Poc at Line 3), and one for flushing L1 instruction cache (invalidate\_I\_PoU at Line 5). In addition, three data synchronization barriers are called (dsb at Line 2, 4, 6) before and after the function calls for flushing L1 D- and I-cache.

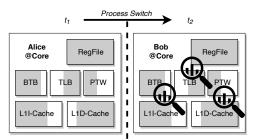

Figure 3 further depicts the dynamic instruction overhead resulted by seL4's flushing mechanism "cleanInvalidateL1Caches" in Figure 2. Since we only consider L1 caches in this example, the resultant overhead is lower than the actual overhead of core-level flushing. The overhead (y-axis) is shown as a function of flushing frequency (x-axis). First, we estimate the dynamic instruction count of executing cleanInvalidateL1Caches on ARMv8, by analyzing the relevant code segments (referencing the functions in Figure 2) in objdump output of the seL4. The size of the main loop in cleanInvalidate\_D\_PoC

<sup>&</sup>lt;sup>1</sup>riscv.org

Figure 3: Estimated instruction count overhead of flushing mechanism in Figure 2 as a function of flushing frequency (100 Hz to 50 KHz) in one SPECint program, with two clock frequencies (100 MHz and 1 GHz).

depends on the cache configuration of L1 D-cache in the system — the number of sets nsets and the number of ways assoc. Here, we assume the L1 D-cache has the following configuration: nsets = 64 and assoc = 8.

Based on the above assumption, the total count of dynamic instructions for flushing operation in a program is approximated in the following way: 1) the dynamic instruction count and cycle count of normal program execution are obtained via FPGA emulation; 2) operating frequency, flushing frequency, and cycle count are used to calculate the number of flushes performed during the program execution; and, 3) the total dynamic instruction count of flushes is normalized to the total dynamic instruction count of normal program execution.

To briefly envision the scaling of the overhead, we consider two representative operating clock frequencies, 100 MHz and 1 GHz, as well as one SPECint2006 workload, 458.sjeng. The flushing frequency is defined as  $x \in [100, 50000]$  Hz, considering the values that are potential and is adopted in practice [13,44]. To contrast with the existing flushing mechanism, we also estimate the overhead with the optimal flushing mechanism in theory, which realizes the complete flushing operations in one instruction, for 458.sjeng. The optimal mechanism is denoted as "opt" (whereas "norm" denotes normal system) for the first element in the tuple in the legend of Figure 3.

# 2.2 Observation

Figure 3 provides two principal observations: First, the dynamic instruction count overhead can become substantial as flushing frequency increases. In the case of 100 MHz clock frequency, core-level flushing incurs about 10% overhead with 1 KHz flushing frequency and almost 100% overhead when approaching 10 KHz. For 1 GHz clock frequency, the same flushing frequency results in much fewer occurrences of flushing. Hence, the overhead is less prominent, however still reaches 10% at 10 KHz and approaching 100% at 50 KHz. Second, the optimal design of flushing mechanism can lead to a sharp decrease of orders-of-magnitude in dynamic instruction count overhead. Such a huge gap between "opt" and "norm" suggests significant promise in performance and power efficiency. Flushing operations are

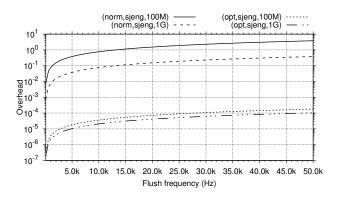

Figure 4: MTA mitigation (temporal isolation) at OS level.

performed during context switches. Context switches usually lead to refilling the on-core state (e.g., caches), therefore, the cold state, caused by the flushing during context switches, incurs minimal additional performance overhead [13].

The aforementioned observations and discussion strongly motivate the design of a special compound instruction to efficiently flush the core-level state residing in multiple components in processor architecture.

# 3. BACKGROUND

# 3.1 Threat Model

The threat model in this study is defined below and is similar to the ones defined in existing advanced microarchitectural timing attacks [24] and research [13]: 1) the adversary Bob is assumed to have control of a user process, which shares the same processor core with the victim Alice's process, in a contemporary preemptive operating system; 2) based on time-sharing mechanisms (e.g., preemption), Bob aims to manipulate the core-level state, such as L1 caches, to exploit the temporal dependence of the state (e.g., cache contention) between Bob and Alice's time slice, hence rendering the timing channels; 3) Bob is capable of designing the point of time to invoke the preemption or inter-process interrupt (IPI), such as the attack discussed in [30], to carefully target a specific part of Alice's execution; and, 4) the system is equipped with necessary temporal isolation mechanisms for protecting L2 caches and LLC, such as [13].

# **3.2** Temporal Isolation

As shown in Figure 4, temporal isolation [7] prevents temporal interference, hence eliminates timing channels, by spatially or temporally partitioning the hardware resources. Existing OS-level temporal isolation methods generally use cache partitioning (page coloring) for shared large caches, such as L2 and last-level cache (LLC), which typically are indexed by the physical address. This way is also referred as spatial partitioning.

However, applying cache partitioning to core-level "private" resources, e.g., L1 caches and TLB, which are indexed by virtual address is difficult. For enforcing temporal isolation in these components, flushing is advocated to cleanse the state in these components [13]. By cleansing the state, there will be no residual state left by the victim for the attacker to create timing channels. This way is also called temporal partitioning.

Table 1: Support for core-level flushing in existing ISAs

(light gray: overkill; dark gray: underkill)

| ISA   | L1DC    | L1IC     | TLB        | BP       |

|-------|---------|----------|------------|----------|

| x86   | wbinvd  | wbinvd   | invpcid    | indirect |

| ARM32 | dccisw  | iciallu  | tlbiall    | bpiall   |

| ARM64 | dc cisw | ic iallu | tlbi allex | n/a      |

The frequency of core-level state flushing is determined by the temporal isolation scheme. The seL4's time protection [13] initiates flushing upon every security-domain switch, which is approximately once per 10-100 milliseconds. seL4's domain is a group of threads, and hence, less frequent than the thread switch. The attack from the threads in the same domain is presumed to not happen. In other schemes, such as Düppel [44], flushing is performed as noise injection to prevent cache timing channel. Therefore, flushing is activated "at least 50 times per millisecond".

# 3.3 Existing ISA Support for Flushing

In existing temporal-isolation systems [13], the implementation of the flushing mechanism is based on existing instructions, such as cache maintenance instructions, provided by the ISA. Table 1 shows how the flushing operations at core level can be implemented with ARM and x86 architectures.

**x86 ISA support for flushing:** clflush invalidates and writes back (if dirty) the cacheline that contains the virtual address specified with the source operand for entire cache hierarchy (data and instruction). clflush is not privileged, and can be executed in user mode. wbinvd invalidates and writes back (if dirty) cachelines for entire cache hierarchy. wbinvd is privileged, and can only be executed in system mode. invlpg invalidates any TLB entries specified with the source operand. invlpg is privileged, and cannot be deployed in user programs. invpcid invalidates mappings in the TLBs and paging-structure caches based on register operand. x86 has no dedicated instruction to flush the state in branch prediction unit (BPU). To achieve BPU cleansing, the indirect branch control feature [21] must be adopted.

ARM ISA support for flushing: dc\_cisw invalidates and writes back the specified individual data cacheline (in set/way format, instead of virtual address format) at the specified cache level for ARM64 (aarch64). dccisw is one of ARM's cache maintenance instructions. This instruction is privileged and hence must be executed in system mode. The equivalent instruction for ARM32 (aarch32) is dccisw. ic\_iallu invalidates entire L1 I-cache (to the point of unification, i.e., L2) for ARM64 (aarch64). This privileged instruction also invalidates BPU. The equivalent instruction for ARM32 is iciallu. tlbi\_allex ( $x \in \{1, 2, 3\}$ ) invalidates all entries in TLB for the specified translate regime (i.e., EL1, EL2, EL3). This set of instructions are ARM64 system instructions, while the ARM32 equivalent is one instruction, tlbiall. bpiall is an ARM32 system instruction, which invalidates all the entries in BPU. The ARM64 equivalent does not exist.

**RISC-V ISA support for flushing:** As an emerging ISA, RISC-V ISA is rapidly including new instructions. There are

two privileged instructions for flushing:<sup>2</sup> 1) fence.i for synchronizing the instruction and data streams, which essentially flushes the L1 I-cache; 2) sfence.vma for flushing the TLBs.

# 4. SIMF MECHANISM

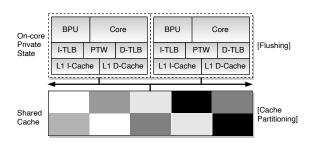

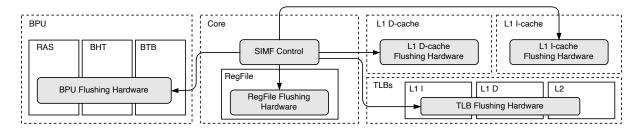

As shown in Figure 5, SIMF mechanism design includes: 1) hardware of flushing operations for each on-core state; 2) the control logic, which manages the issue order of the flushing operations; and, 3) the instruction deployment in software.

In this paper, for the sake of brevity, we consider an inorder scalar processor architecture as the base system, which does not include prefetcher hardware. However, the implementation would not be too onerous for an out of-order processor. The principles remain similar.

# 4.1 Sphere of Flushing

Taking into account the study in [14], about microarchitectural timing channels, SIMF targets a comprehensive set of states on-core, which we define as the sphere of flushing (SoF). SoF includes all the on-core state, L1 D-Cache, L1 I-Cache, TLB and the BPU.

L1 D-Cache is prone to timing channel [19]. Cache access time can vary substantially depending on whether the access is a hit or miss. An attacker can exploit the access time variation to mount timing channel attacks, for example, as shown using PRIME+PROBE [32, 34].

**L1 I-Cache** is similar to L1 D-cache, in terms of cache time access variation. The main difference is that L1 I-cache timing attack relies on creating cache contention via carefully crafted control flow and seeks to leak the execution flow of the victim process (e.g., cryptographic algorithms) [1].

**TLB** timing channel can be constructed by exploiting the time variation of a virtual address translation between TLB hit and miss [15, 20] for control flow (instruction TLB) and data flow (data TLB). We assume a contemporary two-level TLB microarchitecture (e.g., Intel Nehalem<sup>3</sup> and RISC-V Rocket []).

**BPU** incurs varied time cost between a correct and wrong prediction. An attacker can mount the timing channel attack based on this time variation to obtain the execution flow of the victim process [2].

**RegFile** is not targeted by existing OS-level techniques [13]. It has been discussed as a source of exploitable time variation, when there are data dependencies between registers [10], as well as can leak the data stored in the registers [37].

## 4.2 Flushing Operations

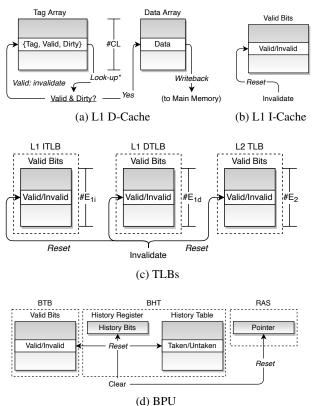

Figure 6 depicts SIMF's flushing operations targeting the components in SoF. Depending on the microarchitecture of each component, the flushing operations vary.

**Flushing L1 D-cache** (Figure 6a) mainly aims to flush the valid and dirty bits. These bits represent validity and coherency status of each cache line. Due to data coherence,

<sup>&</sup>lt;sup>2</sup>Rocket chip recently added an optional L1 d-cache flushing instruction, CFLUSH.D.L1, which is "only for power-down" and "... only supported on systems without S-mode." This instruction is not available in the version of rocket chip used in this paper.

<sup>&</sup>lt;sup>3</sup>www.intel.com/pressroom/archive/reference/ whitepaper\_Nehalem.pdf

Figure 5: Single-instruction multiple-flush mechanism overview.

(u) DI C

Figure 6: SIMF flushing operations.

clearing each cache line's valid bits and dirty bits must be performed along with write-back operation, if the cache line is dirty. Therefore, the entire L1 D-cache flush includes three sub-operations: 1) look up the cache line status corresponding to one selected cache line from the tag array; 2) write back the cache line, if it is dirty; and, 3) resetting the valid and dirty bits. These steps must be done for every cache line in the cache, which totals to #CL. Hence, L1 D-cache flushing comprises N (N =#CL) sequences of the sub-operations mentioned above.

**Flushing L1 I-cache** (Figure 6b) is a simple form of flushing L1 D-cache, since it is not necessary for I-cache to maintain coherence. Flushing L1 I-cache operation only needs to invalidate or reset the valid bits, where each bit maps to one cache line.

Flushing TLBs (Figure 6c) includes flushing TLBs at

Level 1 and Level 2. This TLB system includes separate L1 TLBs for instruction (L1 ITLB) and data (L1 DTLB) and one unified L2 TLB (L2 TLB). TLB flushing operation aims to clean the valid bits for each TLB entry.

We assume BPU uses two-level adaptive branch prediction [43]. The operation for **flushing BPU** (Figure 6d) is composed of three major sub-operations as follows: 1) flushing branch target buffer (BTB) aims to clear the valid bits in BTB; 2) flushing branch history target (BHT) is more complex than BTB, where the history bits in the history register and the entries in the history table are to be cleared; and, 3) flushing return address stack (RAS) can be realized by resetting the stack pointer, which indicates that the RAS is empty.

**Flushing RegFile** aims to remove the user data directly from RegFile. Given a RegFile consisting of #Regs registers, #Regs registers are cleared. In addition, for maintaining the program's correctness, RegFile flushing must be carefully operated after the registers are saved in cache/memory. Vice versa, the registers need to be recovered after flushing, before continuing the program execution. Hence, the context switch (for process switch) is a convenient point of time, when RegFile flushing can be performed.

#### 4.3 Merging Flushing Operations

Based on the design of the flushing operations with respect to the SoF components, SIMF control is realized by merging these operations into one instruction.

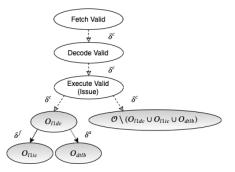

Operation merging or fusion problem can be briefly defined as follows: Given the set of predefined flushing operations (FOs), noted as  $\mathcal{O} = \{O_1, O_2, ..., O_N\}$  and pipeline stages  $\mathcal{S} = \{S_1, S_2, S_3, ..., S_M\}$ , scheduling  $O_i$  into pipeline stage  $S_j$ .

Figure 7 summarizes the design constraints, represented as control and data dependencies, which must be considered when merging flushing operations in one instruction. The control dependencies are denoted as  $\delta^c$ . The data dependencies are denoted as  $\delta^f$  for flow/true dependency, also known as read-after-write (RAW), as well as  $\delta^a$  for anti-dependency, a.k.a. write-after-read (WAR). SIMF considers two main data dependencies: 1) Flushing L1 I-cache ( $O_{l1ic}$ ) will cause refilling the instructions, whose newest version might be in the L1 D-cache and hence depends on flushing L1 D-cache ( $O_{l1dc}$ ); and, 2) Flushing L1 D-cache might require address translation in D-TLB, which will be flushed by  $O_{dtlb}$ .

Table 2 depicts how the proposed SIMF merges the flushing operations  $\mathcal{O}$ , assuming a classic 5-stage pipeline  $\mathcal{S} = \{S_{IF}, S_{ID}, S_{EX}, S_{ME}, S_{WB}\}$ . Given the constraints, we aim to

Figure 7: Dependency graph for flushing operations in SIMF ("\": set minus).

Table 2: SIMF scheduling in a classic 5-stage pipeline based on dependencies in Figure 7 (CCs: clock cycles,  $\alpha$ : cycles per cacheline)

Table 3: SIMF Pipeline Control (SIMF instruction highlighted in gray)

| $\mathbf{I} \setminus \mathbf{T}$ | CC <sub>0</sub> | $\mathbf{CC}_1$ | $\mathbf{CC}_2$ | $\mathbf{CC}_3$ | $\mathbf{CC}_4$ | $\mathbf{CC}_5$ | $\mathbf{CC}_6$ | $\mathbf{CC}_7$ | <b>CC</b> <sub>8</sub> |

|-----------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------------|

| i <sub>0</sub>                    | IF<br>×<br>×    | ID              | EX              | ME              | WB              | ×               | ×               | $\times$        | ×                      |

| <b>i</b> <sub>1</sub>             | $  \times$      | IF              | ID              | $\bigcirc$      | Ò               | <b>\EX</b>      | ME              | WB              | $\times$               |

| <b>i</b> <sub>2</sub>             | $  \times$      | $\times$        |                 |                 |                 |                 |                 |                 | ` <b>▲</b> IF          |

ME in SIMF instruction  $\mathbf{i}_1$  can take multiple cycles.

○: insert pipeline stall.

: kill/delay the following instruction.

schedule the FOs as late as possible (ALAP), which is equivalent to prioritizing issuing the FOs near the commit (i.e., write-back) stage. The first three stages are not considered given the control constraints (flushing must not start before valid execute/issue stage).  $O_{l1dc}$  is scheduled one stage earlier than the other operations ( $\mathcal{O} \setminus O_{l1dc}$ ) to ensure that the dependencies are satisfied.

# 4.4 SIMF Pipeline Control

Table 3 illustrates the pipeline control mechanism for SIMF with a classic pipeline time table. Column 1 shows the instruction sequence executed from top  $(i_0)$  to bottom. Row 1, shows the clock cycles starting from the left (**CC**<sub>0</sub>) to right. In each clock cycle, at least one pipeline stage, i.e., IF, ID, EX, ME, and WB, is executed, unless the instruction is stalled (denoted as " $\bigcirc$ ") or delayed (" $\square$ "). As shown in Table 3, for maintaining the program's correctness after flushing, SIMF  $(i_1)$  needs additional pipeline control mechanism to guarantee: 1) all the prior instructions must have been committed before flushing, which is denoted as  $i_0.WB \rightarrow i_1.EX$ ; and, 2) all the following instructions must observe the resultant state of the components in SoF, which have been flushed, i.e.,  $i_1.WB \rightarrow i_2.IF$ .

Table 4: RISC-V System configuration

Attribute

| Attribute | Setting         |

|-----------|-----------------|

| ISA       | GC (IMAFDC)     |

| L1D-Cache | 32KiB 8-way 64B |

| L1I-Cache | 32KiB 8-way 64B |

| L1D-TLB   | 32              |

| L1I-TLB   | 32              |

| L2-TLB    | 128             |

| BTB       | 28              |

| BHT       | 512             |

| RAS       | 6               |

| RAM       | 256MiB          |

|           |                 |

## 4.5 SIMF Software

SIMF can be deployed in software depending on the temporal isolation schemes. In this paper, we discuss two potential SIMF based temporal isolation schemes, which both use SIMF in kernel space (as a privileged instruction).

**Aggressive scheme:** Similar to [44], where even the kernel space is not trusted, the SIMF instruction can be deployed at the boundary between the switch from user space to kernel space, and the switch from kernel space to user space. This way ensures that every kernel/user switch will incur flushing, even if there will be no process switch. Such a scheme creates a strict temporal isolation and can introduce high overhead due to much more frequent activation of flushing operations.

**Moderate scheme:** Similar to [13], the SIMF instruction can be integrated in the software path where process/thread switch occurs, for instance, when the current security domain switches to another security domain in seL4 microkernel. This scheme will incur fewer flushing operations, while relying on the security assumptions provided by the security policy of the operating system.

Additional instructions are needed for RegFile flushing, to ensure the context will not be lost. If SIMF is deployed in the software path where context is saved, such as the trap entry of the operating system, the extra instructions needed will be much fewer. A few instructions are still required to be added to load back the values of the registers, which are needed for the system binary interface (SBI). Hence, for ease of deployment, register file flushing can be disabled.

# 5. EVALUATION

In this section, we evaluate SIMF on a RISC-V processor, implemented on an FPGA with various workloads to answer the following questions.

How expensive the hardware cost is with SIMF implemented (§5.1)?

What is the performance penalty for the worst case, that is when L1 D-cache is full (§5.2)?

How SIMF performs when inserted into a state-of-art microkernel (§5.4)?

How much does SIMF slow down a contemporary Linux kernel with SMP in a multi-core scenario (§5.5)?

How much does SIMF affect user programs (§5.3)?

What is the security enhancement (§5.6)?

To check the efficacy of SIMF, we implement the proposed SIMF as a new instruction, FLUSHX, in the Rocket core (i.e., in-order scalar RV64GC implementation of RISC-V ISA), which comes with Rocket Chip SoC (multi-core-capable and with hardware support for coherence) [].

Table 5: FPGA utilization of FLUSHX and baseline system @180 MHz. The overhead in brackets is without  $O_{rf}$ .

| Resource | Baseline | Flushx | w/o $O_{rf}$ | Overhead     |

|----------|----------|--------|--------------|--------------|

| LUT      | 37595    | 40107  | 38323        | 6.7% (1.9%)  |

| F/F      | 16928    | 19436  | 17436        | 14.8% (3.0%) |

| BRAM     | 49       | 49     | 49           | _            |

| DSP      | 15       | 15     | 15           | -            |

| I/O      | 3        | 3      | 3            | -            |

| BUFG     | 2        | 2      | 2            | -            |

| MMCM     | 1        | 1      | 1            | -            |

Table 6: Core-level flushing performance (ARMv8 implementation is hard IP of Cortex-A53 on ZCU102; RV64GC implementation is soft core on ZCU102; Intel x86 Haswell and ARMv7 Cortext-A9 in Yellow are obtained from [13])

| Arch.  | FO              | #Cycles | #Dyn. Instr. | SoF        |

|--------|-----------------|---------|--------------|------------|

| x86    | Indirect        | 91800   | -            | L1-D&I     |

| ARMv7  | dccisw/iciallu  | 36000   | -            | L1-D&I     |

| ARMv8  | dc_cvau/ic_ivau | 91299   | 63719        | L1-D&I     |

| RV64GC | FLUSHX          | 16025.5 | 136          | Core-level |

We use a Xilinx ZYNQ Ultrascale+ FPGA (ZCU102) board to implement the RISC-V processor(s), which technologyadvanced and has greater amount of resources than the existing FPGA boards (e.g., ZC702, Zedboard, and ZYBO FPGAs) targeted by the original Rocket chip's FPGA build. We ported the original repository of Rocket chip's FPGA build to ZCU102. SIMF (FLUSHX) is implemented into the rocket core with the configuration specified in Table 4.

# 5.1 Hardware Cost

The FPGA synthesis is performed with Vivado v2017.1 using default strategy.

Table 5 depicts the hardware cost, in terms of FPGA resources when the FLUSHX instruction is implemented. The major FPGA resources utilized include CLB LUTs, CLB flip/flops (F/Fs), block RAMs (BRAMs), DSPs (implementing arithmetic cells), physical input/output ports (IO), clock buffers (BUFG), and mixed mode clock manager (MMCM). This result shows that supporting FLUSHX instruction mainly increases the total LUTs (by 6.7%) and F/Fs (by 14.8%). We also observe that FLUSHX without  $O_{rf}$  (equivalent to the complete functionality of existing temporal isolation) has minimal overheads (1.9% LUTs and 3.0% F/Fs). The maximum clock frequency for FLUSHX is 187 MHz and for the baseline is 195 MHz.

## 5.2 Flushing Overhead

The first case study aims to measure the performance overhead of the proposed core-level SIMF in comparison to the contemporary ISA support. The test program is manually designed to: one, construct and fill a cache-sized contiguous memory space (via mmap()); and, two, execute the core-level flush.

Table 6 shows the comparison of overhead for core-level flushing between FLUSHX in the RISC-V processor and ARM Cortex-A53 using existing methods. ARM core flush is executed by calling \_\_clear\_cache(), which targets the cache-sized memory space, provided by Linux to the user space, which is implemented in the same manner as the software

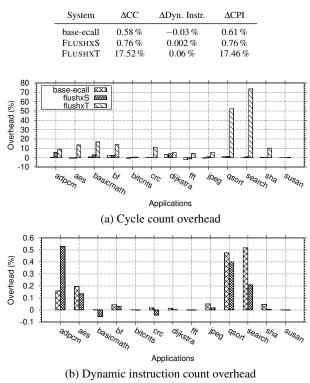

Figure 8: Median performance overhead (in percentage) of running MiBench.

functions in Figure 2. \_\_clear\_cache() essentially performs dc\_cvau, i.e., data cache clean by virtual address (VA) to the point of unification (PoU), i.e., L2, and ic ivau (instruction cache invalidate by VA to the PoU) instructions to flush L1 D-cache and I-cache.

The results on the ARM are obtained by perf. The test program is run 15,000 times to reduce the standard deviation, i.e., 593.5 (0.65%) clock cycles and 249.9 (0.39%) instructions. The result of RISC-V is obtained via inserted rdcycle and rdinstret instructions. The standard deviation for 100 runs of RISC-V is 82.1 clock cycles (0.51%) and 0 instructions.

FLUSHX finishes flushing the complete core-level state with about 1/5 of the clock cycles used by ARMv8 (using user-mode flushing instructions), as well as about 1/2 and 1/5 clock cycles of ARMv7 and x86, reported in [13]. FLUSHX reduces dynamic instruction count by a factor of 468, in comparison to ARMv8 (using user-mode flushing instructions).

## 5.3 User Program Benchmark

To observe the runtime overhead of executing FLUSHX instruction in real-world user programs, we test our systems using a representative embedded application benchmark suite, MiBench [16]. We test FLUSHX with two scenarios: 1) FLUSHXS incur a FLUSHX via a syscall (similar to moderate scheme); and, 2) FLUSHXT incur FLUSHX at every kernel/user crossing (similar to aggressive scheme). The benchmark suite is run on a simple application execution environment (riscv-pk), which provides user programs with

Table 8: seL4 kernel scheduling overhead. RISC-V runs seL4 v10.1.1 kernel with seL4test workloads. In scheduling function, four execution paths incurring thread switch are measured respectively. ARM data in yellow is obtained from [13] measuring domain switch time.

| Arch.            | FO                  | #Cycles mean $\pm$ std.                | #Dyn. Instr.<br>mean $\pm$ std.                                       |

|------------------|---------------------|----------------------------------------|-----------------------------------------------------------------------|

| ARMv7<br>ARMv7   | -<br>Ge et al. [13] | $560 \pm 1\%$<br>21600 + 1%            | -                                                                     |

| RV64GC<br>RV64GC | FLUSHX              | $940.5 \pm 318.7 \\ 8568.1 \pm 3738.5$ | $\begin{array}{r} 432.8  \pm  155.3 \\ 436.9  \pm  147.1 \end{array}$ |

POSIX syscall services. riscv-pk is customized to deploy FLUSHX in a new syscall and trap entry. For each program, we execute the program 50 times (standard deviation  $\leq 1\%$ ).

As shown in Table 7, performing FLUSHX instruction once per execution (FLUSHXS) incurs negligible overhead in both clock cycles and dynamic instruction count (within the margin of error), especially when compared to pure syscall overhead ("base-ecall"). Performing FLUSHX aggressively at every entering kernel space (FLUSHXT) can substantially increase the execution time and CPI by 15%. The main reason for the difference of overhead between FLUSHXS and FLUSHXT is that FLUSHXT scheme activates a greater number of FLUSHX execution in these programs from the original system calls. These system calls do not include FLUSHX in the execution path at runtime in FLUSHXS system.

Figure 8a and 8b depict the detailed view of the overhead for each benchmark application. For cycle overhead (shown in Figure 8a), among all the benchmark programs, there are two prominent cases, where FLUSHXT incurs a substantial cycle overhead. These are in stringsearch search (around 70%) and quick sort qsort (roughly 50%). The reason is that these two programs proportionally have more syscalls. In some cases, e.g., bitcounts bitcnts, FFT fft, and JPEG jpeg, the cycle overhead is negative, because the overhead is negligible within the range of standard deviation (due to cache and branch prediction behaviors). For dynamic instruction count, the overhead is negligible across all the benchmark programs.

## 5.4 seL4 Microkernel

To observe the system-level manifestation of SIMF in a real-world microkernel. We added FLUSHX into seL4 microkernel (v10.1.1), which is a security-oriented capability-based microkernel. We insert FLUSHX instruction into functions for thread switch, such as switchToThread() and switchToIdleThread(). seL4's domain switch is a special case of thread switch, which largely follows the same execution path as thread switch.

To quantify the performance of SIMF, we measured the cost of scheduling, where thread switch is invoked, with the seL4test as the workload. seL4test is composed of 100 testing programs, each of which targets one set of seL4 properties. During the execution of seL4test, schedule() is called 3,496,281 times, while 427,189 events of thread switch are incurred during schedule. Both systems with and without FLUSHX finish the seL4test correctly, with the same output score.

Table 8 shows the total clock cycles and dynamic instruction count of scheduling for the system with and without

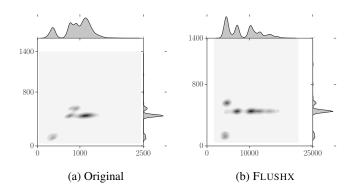

Figure 9: Distribution of seL4 kernel scheduling cost with thread switch incurred, w/ and w/o FLUSHX. X-axis is cycle count. Y-axis is dynamic instruction count. The colored area in X-Y plane denotes the two-dimensional density function from kernel density estimation (KDE). The shaded curves in the marginal area at top and right denote one-dimensional density function with respect to X and Y.

FLUSHX instruction implemented, in comparison to the domain switch cost reported in [13], where ARMv7 's flushing mechanism is adopted. The cycle count of ARMv7 is calculated based on time and clock speed reported. On average, ARMv7's ISA support results in about 38.57x overhead (in comparison to the baseline) in clock cycles, while FLUSHX incurs less than 10x cycle overhead with 4 additional instructions. As shown in Figure 9, the cycle cost varies depending on the actual execution path in scheduling (some paths are affected more by FLUSHX). The distribution of the dynamic instruction count is minimally affected by FLUSHX.

## 5.5 Linux with Imbench

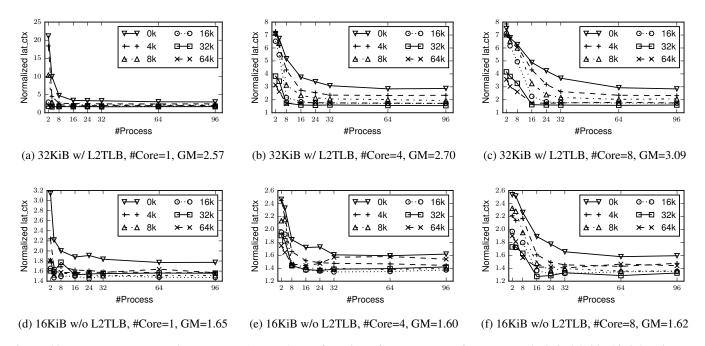

We choose RISC-V Linux kernel v4.20 and add FLUSHX into the thread switch procedure \_\_switch\_to. We test the FLUSHX Linux and compare with the baseline Linux kernel by running lmbench [29]. For both systems, we create three types of hardware, composing 1 core, 4 cores, and 8 cores, each with two configurations of caches (16 KiB and 32 KiB) and TLBs (with and without L2 TLB).

Figure 10 shows the overhead of context switch latency due to FLUSHX. For larger caches and TLBs, FLUSHX incurs more overhead with a smaller working set and fewer processes. Using smaller caches and TLBs leads to much smaller flushing overhead (almost 1/2 in 8-core system). It is also seen that as processes increase, the overhead will approach 50% (for large caches and TLBs) or less (for small caches and TLBs). The worst-case overhead is witnessed in an extreme scenario, where two processes runs on one core with larger caches and TLBs, computing with a very small working set (0KB).

# 5.6 Temporal Isolation Test

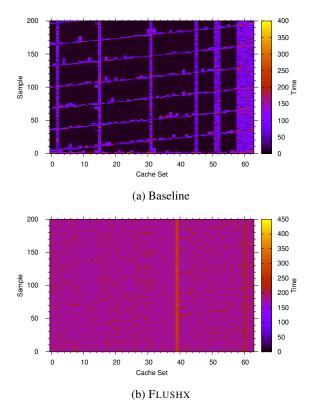

To evaluate the effects of FLUSHX instruction in face of timing channel attacks, we implement a classic L1 D-cache attack, namely Prime+Probe based on the open-source tool called Mastik [41]. We port Mastik to RISC-V to mount Prime+Probe cache timing attacks.

Figure 10: Imbench contex switch latency (lat\_ctx) as a function of the number of processes (2, 4, 8, 16, 32, 64, 96), with different size of working set, normalized to the baseline. GM: geometric mean. RISC-V Linux kernel version is 4.20 with FLUSHX inserted in \_\_switch\_to(). Each line represents a working set size in the legend.

Figure 11: Timing channel of L1 D-cache by Prime+Probe.

We create a simplified attack using lightweight proxy kernel, PK (riscv-pk). We implement the victim program as a dedicated system call. The content of the victim program is a patterned data cache access, adapted from the example code from Mastik. FLUSHX is inserted before returning to attacker' process on FLUSHX core. We modify the attack program to raise this special system call, after cache prime is finished. The probed samples are set to 20,000, which is sufficient to witness the significance of the cache channels.

Figure 11a and 11b illustrates the samples from Sample 1 to 200, in the cache timing attack, on the baseline and FLUSHX systems, respectively. The clear cache behavior patterns of cache set accesses can be observed for the unprotected baseline system, where the cache set hit (less than 10 cycles of cache access time, in black) and miss (more than 50 clock cycles of access time in purple) can be differentiated. Figure 11b shows that the protected system, which executes FLUSHX before returning to the attacker's process, and can cleanse the residual state (all cache misses) in the L1 D-cache.

# 6. RELATED WORK

Timing attack countermeasures have been proposed at differing layers of the computing stack, from hardware right up to the application layer.

Hardware-based countermeasures [33,35,38,39,40] mostly focus on redesigning the cache against cache based timing channel attacks. The work in [33] enforces cache partitioning to remove cache contention. Newcache [39] introduces randomized mapping in replacement of cache partitioning for better flexibility. CEASE/CEASER [35] uses encrypted cache addressing scheme to implement efficient randomization. [38] and ScatterCache [40] extends encryption-based randomization to combine cache address and process ID as encryption input. Aiming at speculation-based side channel attacks, CleanupSpec [36] modifies cache policies and coherency management on system bus, in order to roll back the cache state after miss-speculation. These methods extensively modify the original cache operations, largely target cache timing attacks at the last level cache (LLC), and are evaluated in abstract models using system simulators (e.g., GEM5 [4]). No hardware implementation has been reported. Another line of hardware-based countermeasures [12, 26] seek to eliminate timing channels by enforcing information flow tracking in hardware. These methods introduce new hardware description languages and usually incur additional memory elements for security tags.

**Software-based** methods are usually implemented in hypervisors, operating systems, or applications. These methods can categorized as follows: Based on time measurement, FuzzyTime [18] and TimeWarp [28] adds intentional noise to the system clock so as to prevent the adversary from accurately measure the timing of microarchitectural events. The time noise will also affect the original programs system-wide, wherever accurate time is required. StealthMem [11, 22] implements spatial partitioning to enforce information isolation in LLC against timing attacks.

**Flushing** mechanism has been adopted by a variety of OSlevel software-based countermeasures [13, 44]. Düppel [44] uses flushing of private L1 and L2 caches to inject timing noise so as to maximize the difficulty of mounting cachebased timing attacks. Düppel assumes the attackers can perform a probe as frequently as every 50,000 (about 60 KHz at 3 GHz clock speed) to 90,000 CPU cycles. Ge et al [13] leverages core-level flushing along with L2 and LLC cache partitioning to minimize the available timing channels in all the microarchitectural components. The flushing is assumed to be performed at every domain switch.

Varys [31] uses flushing for cleansing private L1 and L2 caches, to protect Intel SGX enclave from various timing channel attacks, assuming the extreme case that privileged software is controlled by the attacker. The flushing is performed at the frequency of 100 Hz, 5.5 KHz, and 10 KHz. For 100 Hz, Varys incurs 19% drop-down in throughput of Nginx due to indirect flushing in Intel ISA.

MI6 [6] is an enclave design for out-of-order RISC-V processors, which also includes a **purge** instruction to flushing on-core state (excluding register-file) upon (de)scheduling. SIMF differs to MI6 in several aspects: MI6 is specific to only RiscyOO processor and cannot be generalized, while SIMF can be implemented for any in-order processor; MI6 relies on the specific features of the baseline processor RiscyOO and does not have the mechanism to actually clean replacement tags in caches and TLBs; MI6 does not actually clean some microarchitectural states (e.g., issue queue), which may well be exploited by novel attacks; and, MI6's flushing mechanism does not write back the dirty cache lines, hence, it does not work for caches with write-back policy (which is dominant in real-world modern processors).

# 7. CONCLUSION

In this paper, we have presented SIMF, a new ISA extension to support efficient temporal isolation. SIMF is capable of flushing core-level state in one instruction execution and can be integrated with OS-level timing attack mitigation. We have prototyped SIMF as a FLUSHX instruction on RISC-V processor and evaluated on FPGA with a real-world micro-kernel, Linux kernel, user programs, and Prime+Probe cache timing attack. Our evaluation shows that SIMF removes the timing channels effectively with significantly less clock cycles and dynamic instruction count.

#### REFERENCES

- O. Aciiçmez, "Yet another microarchitectural attack:: Exploiting i-cache," in *Proceedings of the 2007 ACM Workshop on Computer Security Architecture*, ser. CSAW '07. New York, NY, USA: ACM, 2007, pp. 11–18. [Online]. Available: http://doi.acm.org/10.1145/1314466.1314469

- [2] O. Actiçmez, S. Gueron, and J.-P. Seifert, "New branch prediction vulnerabilities in openssl and necessary software countermeasures," in *Cryptography and Coding*, S. D. Galbraith, Ed. Berlin, Heidelberg: Springer Berlin Heidelberg, 2007, pp. 185–203.

- [3] K. Asanović, R. Avizienis, J. Bachrach, S. Beamer, D. Biancolin, C. Celio, H. Cook, D. Dabbelt, J. Hauser, A. Izraelevitz, S. Karandikar, B. Keller, D. Kim, J. Koenig, Y. Lee, E. Love, M. Maas, A. Magyar, H. Mao, M. Moreto, A. Ou, D. A. Patterson, B. Richards, C. Schmidt, S. Twigg, H. Vo, and A. Waterman, "The rocket chip generator," EECS Department, University of California, Berkeley, Tech. Rep. UCB/EECS-2016-17, Apr 2016. [Online]. Available: http: //www2.eecs.berkeley.edu/Pubs/TechRpts/2016/EECS-2016-17.html

- [4] N. Binkert, B. Beckmann, G. Black, S. K. Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R. Hower, T. Krishna, S. Sardashti, R. Sen, K. Sewell, M. Shoaib, N. Vaish, M. D. Hill, and D. A. Wood, "The gem5 simulator," *SIGARCH Comput. Archit. News*, vol. 39, no. 2, pp. 1–7, Aug. 2011. [Online]. Available: http://doi.acm.org/10.1145/2024716.2024718

- [5] P. Bose, D. Brooks, A. Buyuktosunoglu, P. Cook, K. Das, P. Emma, M. Gschwind, H. Jacobson, T. Karkhanis, P. Kudva, S. Schuster, J. Smith, V. Srinivasan, V. Zyuban, D. Albonesi, and S. Dwarkadas, "Early-stage definition of lpx: A low power issue-execute processor," in *Power-Aware Computer Systems*, B. Falsafi and T. N. Vijaykumar, Eds. Berlin, Heidelberg: Springer Berlin Heidelberg, 2003, pp. 1–17.

- [6] T. Bourgeat, I. Lebedev, A. Wright, S. Zhang, Arvind, and S. Devadas, "Mi6: Secure enclaves in a speculative out-of-order processor," in Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture, ser. MICRO '52. New York, NY, USA: Association for Computing Machinery, 2019, p. 42–56. [Online]. Available: https://doi.org/10.1145/3352460.3358310

- [7] D. Bui, E. Lee, I. Liu, H. Patel, and J. Reineke, "Temporal isolation on multiprocessing architectures," in *Proceedings of the 48th Design Automation Conference*, ser. DAC '11. New York, NY, USA: ACM, 2011, pp. 274–279. [Online]. Available: http://doi.acm.org/10.1145/2024724.2024787

- [8] C. Canella, J. V. Bulck, M. Schwarz, M. Lipp, B. von Berg, P. Ortner, F. Piessens, D. Evtyushkin, and D. Gruss, "A systematic evaluation of transient execution attacks and defenses," in 28th USENIX Security Symposium (USENIX Security 19). Santa Clara, CA: USENIX Association, Aug. 2019, pp. 249–266. [Online]. Available: https: //www.usenix.org/conference/usenixsecurity19/presentation/canella

- [9] D. Cock, Q. Ge, T. Murray, and G. Heiser, "The last mile: An empirical study of timing channels on sel4," in *Proceedings of the* 2014 ACM SIGSAC Conference on Computer and Communications Security, ser. CCS '14. New York, NY, USA: ACM, 2014, pp. 570–581. [Online]. Available: http://doi.acm.org/10.1145/2660267.2660294

- [10] B. Coppens, I. Verbauwhede, K. D. Bosschere, and B. D. Sutter, "Practical mitigations for timing-based side-channel attacks on modern x86 processors," in 2009 30th IEEE Symposium on Security and Privacy, May 2009, pp. 45–60.

- [11] X. Dong, Z. Shen, J. Criswell, A. L. Cox, and S. Dwarkadas, "Shielding software from privileged side-channel attacks," in 27th USENIX Security Symposium (USENIX Security 18). Baltimore, MD: USENIX Association, Aug. 2018, pp. 1441–1458. [Online]. Available: https: //www.usenix.org/conference/usenixsecurity18/presentation/dong

- [12] A. Ferraiuolo, M. Zhao, G. E. Suh, and A. C. Myers, "Hyperflow: A

processor architecture for nonmalleable, timing-safe information-flow security," in *Proceedings of the 2018 ACM SIGSAC Conference on Computer and Communications Security, CCS 2018*, 2018.

- [13] Q. Ge, Y. Yarom, T. Chothia, and G. Heiser, "Time protection: The missing os abstraction," in *Proceedings of the Fourteenth EuroSys Conference 2019*, ser. EuroSys '19. New York, NY, USA: ACM, 2019, pp. 1:1–1:17. [Online]. Available: http://doi.acm.org/10.1145/3302424.3303976

- [14] Q. Ge, Y. Yarom, D. Cock, and G. Heiser, "A survey of microarchitectural timing attacks and countermeasures on contemporary hardware," *Journal of Cryptographic Engineering*, vol. 8, no. 1, pp. 1–27, Apr 2018. [Online]. Available: https://doi.org/10.1007/s13389-016-0141-6

- [15] B. Gras, K. Razavi, H. Bos, and C. Giuffrida, "Translation leak-aside buffer: Defeating cache side-channel protections with TLB attacks," in 27th USENIX Security Symposium (USENIX Security 18). Baltimore, MD: USENIX Association, Aug. 2018, pp. 955–972. [Online]. Available: https: //www.usenix.org/conference/usenixsecurity18/presentation/gras

- [16] M. R. Guthaus, J. S. Ringenberg, D. Ernst, T. M. Austin, T. Mudge, and R. B. Brown, "Mibench: A free, commercially representative embedded benchmark suite," in *Proceedings of the Workload Characterization, 2001. WWC-4. 2001 IEEE International Workshop*, ser. WWC '01. Washington, DC, USA: IEEE Computer Society, 2001, pp. 3–14. [Online]. Available: https://doi.org/10.1109/WWC.2001.15

- [17] J. L. Hennessy and D. A. Patterson, "A new golden age for computer architecture," *Commun. ACM*, vol. 62, no. 2, pp. 48–60, Jan. 2019. [Online]. Available: http://doi.acm.org/10.1145/3282307

- [18] W. . Hu, "Reducing timing channels with fuzzy time," in *Proceedings*. 1991 IEEE Computer Society Symposium on Research in Security and Privacy, May 1991, pp. 8–20.

- W.-M. Hu, "Lattice scheduling and covert channels," in *Proceedings* of the 1992 IEEE Symposium on Security and Privacy, ser. SP '92.

Washington, DC, USA: IEEE Computer Society, 1992, pp. 52–.

[Online]. Available: http://dl.acm.org/citation.cfm?id=882488.884165

- [20] R. Hund, C. Willems, and T. Holz, "Practical timing side channel attacks against kernel space aslr," in *Proceedings of the 2013 IEEE Symposium on Security and Privacy*, ser. SP '13. Washington, DC, USA: IEEE Computer Society, 2013, pp. 191–205. [Online]. Available: http://dx.doi.org/10.1109/SP.2013.23

- [21] Intel, "Speculative execution side channel mitigations," May 2018. [Online]. Available: https://software.intel.com/security-softwareguidance/api-app/sites/default/files/336996-Speculative-Execution-Side-Channel-Mitigations.pdf

- [22] T. Kim, M. Peinado, and G. Mainar-Ruiz, "STEALTHMEM: System-level protection against cache-based side channel attacks in the cloud," in *Presented as part of the 21st USENIX Security Symposium (USENIX Security 12)*. Bellevue, WA: USENIX, 2012, pp. 189–204. [Online]. Available: https://www.usenix.org/conference/usenixsecurity12/technicalsessions/presentation/kim

- [23] G. Klein, J. Andronick, K. Elphinstone, T. Murray, T. Sewell, R. Kolanski, and G. Heiser, "Comprehensive formal verification of an OS microkernel," *ACM Transactions on Computer Systems*, vol. 32, no. 1, pp. 2:1–2:70, Feb. 2014.

- [24] P. Kocher, D. Genkin, D. Gruss, W. Haas, M. Hamburg, M. Lipp, S. Mangard, T. Prescher, M. Schwarz, and Y. Yarom, "Spectre attacks: Exploiting speculative execution," *CoRR*, vol. abs/1801.01203, 2018. [Online]. Available: http://arxiv.org/abs/1801.01203

- [25] B. W. Lampson, "A note on the confinement problem," Commun. ACM, vol. 16, no. 10, pp. 613–615, Oct. 1973. [Online]. Available: http://doi.acm.org/10.1145/362375.362389

- [26] X. Li, V. Kashyap, J. K. Oberg, M. Tiwari, V. R. Rajarathinam, R. Kastner, T. Sherwood, B. Hardekopf, and F. T. Chong, "Sapper: A language for hardware-level security policy enforcement," in Proceedings of the 19th International Conference on Architectural Support for Programming Languages and Operating Systems, ser. ASPLOS '14. New York, NY, USA: ACM, 2014, pp. 97–112. [Online]. Available: http://doi.acm.org/10.1145/2541940.2541947

- [27] M. Lipp, M. Schwarz, D. Gruss, T. Prescher, W. Haas, A. Fogh, J. Horn, S. Mangard, P. Kocher, D. Genkin, Y. Yarom, and M. Hamburg, "Meltdown: Reading kernel memory from user space,"

in 27th USENIX Security Symposium (USENIX Security 18), 2018.

- [28] R. Martin, J. Demme, and S. Sethumadhavan, "Timewarp: Rethinking timekeeping and performance monitoring mechanisms to mitigate side-channel attacks," in 2012 39th Annual International Symposium on Computer Architecture (ISCA), June 2012, pp. 118–129.

- [29] L. McVoy and C. Staelin, "Lmbench: Portable tools for performance analysis," in *Proceedings of the 1996 Annual Conference on USENIX Annual Technical Conference*, ser. ATEC '96. Berkeley, CA, USA: USENIX Association, 1996, pp. 23–23. [Online]. Available: http://dl.acm.org/citation.cfm?id=1268299.1268322

- [30] M. Neve and J.-P. Seifert, "Advances on access-driven cache attacks on aes," in *Selected Areas in Cryptography*, E. Biham and A. M. Youssef, Eds. Berlin, Heidelberg: Springer Berlin Heidelberg, 2007, pp. 147–162.

- [31] O. Oleksenko, B. Trach, R. Krahn, A. Martin, C. Fetzer, and M. Silberstein, "Varys: Protecting sgx enclaves from practical side-channel attacks," in *Proceedings of the 2018 USENIX Conference* on Usenix Annual Technical Conference, ser. USENIX ATC '18. Berkeley, CA, USA: USENIX Association, 2018, pp. 227–239. [Online]. Available: http://dl.acm.org/citation.cfm?id=3277355.3277378

- [32] D. A. Osvik, A. Shamir, and E. Tromer, "Cache attacks and countermeasures: The case of aes," in *Proceedings of the 2006 The Cryptographers' Track at the RSA Conference on Topics in Cryptology*, ser. CT-RSA'06. Berlin, Heidelberg: Springer-Verlag, 2006, pp. 1–20. [Online]. Available: http://dx.doi.org/10.1007/11605805\_1

- [33] D. Page, "Partitioned cache architecture as a side-channel defence mechanism," 2005, page@cs.bris.ac.uk 13017 received 22 Aug 2005. [Online]. Available: http://eprint.iacr.org/2005/280

- [34] C. Percival, "Cache missing for fun and profit," in *Proc. of BSDCan* 2005, 2005.

- [35] M. K. Qureshi, "Ceaser: Mitigating conflict-based cache attacks via encrypted-address and remapping," in 2018 51st Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), Oct 2018, pp. 775–787.

- [36] G. Saileshwar and M. K. Qureshi, "Cleanupspec: An "undo" approach to safe speculation," in *Proceedings of the 52Nd Annual IEEE/ACM International Symposium on Microarchitecture*, ser. MICRO '52. New York, NY, USA: ACM, 2019, pp. 73–86. [Online]. Available: http://doi.acm.org/10.1145/3352460.3358314

- [37] J. Stecklina and T. Prescher, "Lazyfp: Leaking FPU register state using microarchitectural side-channels," *CoRR*, vol. abs/1806.07480, 2018. [Online]. Available: http://arxiv.org/abs/1806.07480

- [38] D. Trilla, C. Hernandez, J. Abella, and F. J. Cazorla, "Cache side-channel attacks and time-predictability in high-performance critical real-time systems," in *Proceedings of the 55th Annual Design Automation Conference*, ser. DAC '18. New York, NY, USA: ACM, 2018, pp. 98:1–98:6. [Online]. Available: http://doi.acm.org/10.1145/3195970.3196003

- [39] Z. Wang and R. B. Lee, "A novel cache architecture with enhanced performance and security," in *Proceedings of the 41st Annual IEEE/ACM International Symposium on Microarchitecture*, ser. MICRO 41. Washington, DC, USA: IEEE Computer Society, 2008, pp. 83–93. [Online]. Available: https://doi.org/10.1109/MICRO.2008.4771781

- [40] M. Werner, T. Unterluggauer, L. Giner, M. Schwarz, D. Gruss, and S. Mangard, "Scattercache: Thwarting cache attacks via cache set randomization," in 28th USENIX Security Symposium (USENIX Security 19). Santa Clara, CA: USENIX Association, Aug. 2019, pp. 675–692. [Online]. Available: https: //www.usenix.org/conference/usenixsecurity19/presentation/werner

- [41] Y. Yarom, "Mastik: A micro-architectural side-channel toolkit," 2016. [Online]. Available: https://cs.adelaide.edu.au/~yval/Mastik/Mastik.pdf

- [42] Y. Yarom, "Micro-architectural side-channel attacks," CHES tutorial, Aug. 2016. [Online]. Available: https://iacr.org/workshops/ches/ches2016/program.php

- [43] T.-Y. Yeh and Y. N. Patt, "Two-level adaptive training branch prediction," in *Proceedings of the 24th Annual International Symposium on Microarchitecture*, ser. MICRO 24. New York, NY, USA: ACM, 1991, pp. 51–61. [Online]. Available: http://doi.acm.org/10.1145/123465.123475

[44] Y. Zhang and M. K. Reiter, "Düppel: Retrofitting commodity operating systems to mitigate cache side channels in the cloud," in *Proceedings of the 2013 ACM SIGSAC Conference on Computer* & Communications Security, ser. CCS '13. New York, NY, USA: ACM, 2013, pp. 827–838. [Online]. Available: http://doi.acm.org/10.1145/2508859.2516741